揭阳SDIO分析仪电话

系统的电流负载能力一般在几个KΩ以上,分流效应对系统的影响一般可以忽略,现在流行的几种长逻辑分析仪探头的阻抗一般在20~200KΩ之间。b、探头的容性负载:容性负载就是探头接入系统时,探头的等效电容,这个值一般在1~30PF之间,在高速系统中,容性负载对电路的影响远远于阻性负载,如果这个值太,将会直接影响整个系统中的信号"沿"的形状改变整个电路的性质,改变逻辑分析仪对系统观测的实时性,导致我们看到的并不是系统原有的特性。c、探头的易用性:是指探头接入系统时的难易程度,随着芯片封装的密度越来越高,出现了BGA、QFP、TQFP、PLCC、SOP等各种各样的封装形式,IC的脚间距小的已达到,要很好的将信号引出,特别是BGA封装,确实有困难,并且分立器件的尺寸也越来越小,典型的已达到×。d、与现有电路板上的调试部分的兼容性。6、系统的开放性:随着数据共享的呼声越来越高,我们所使用的系统的开放性就越来越重要,逻辑分析仪的操作系统也由过去的系统发展到使用Windows介面,这样我们在使用时很方便。小结如果在你的工作中有数字逻辑信号,你就有机会使用逻辑分析仪。因此应选好一种逻辑分析仪,既符合所用的功能,又不太超越所需的功能。协议分析仪/训练器厂家直销就找欧奥!揭阳SDIO分析仪电话

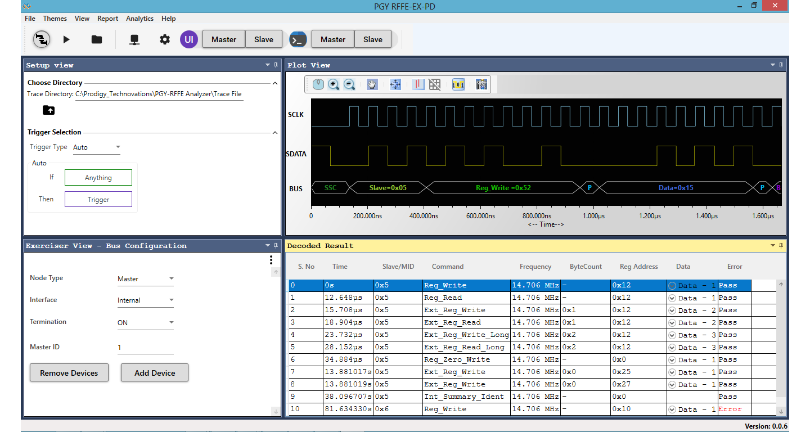

确实有困难,并且分立器件的尺寸也越来越小,典型的已达到×。d、与现有电路板上的调试部分的兼容性。6、系统的开放性:随着数据共享的呼声越来越高,我们所使用的系统的开放性就越来越重要,逻辑分析仪的操作系统也由过去的系统发展到使用Windows介面,这样我们在使用时很方便。小结如果在你的工作中有数字逻辑信号,你就有机会使用逻辑分析仪。因此应选好一种逻辑分析仪,既符合所用的功能,又不太超越所需的功能。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。徐州UFS分析仪价格RFFE协议分析仪/训练器找欧奥!

2、采样频率:采样频率一般设置为被测信号的4~5倍,需要协议解码的时候需要20倍以上,采样率不够会出现解码错误。被测信号频率高要采用同步采样;3、存储深度:通道复用、分段存储、压缩存储、记录模式(实时存储);4、门限电压:一般设置为1/2(MAX+MIN);5、滤波设置:总线滤波,滤一个采样周期的毛刺信号。通道滤波,滤1~2个采样周期的滤波。总线滤波和通道滤波都是硬件滤波。设置效果如图2所示:图2参数设置四、IIC触发与解码设置1、名称设置为自定义;2、输入总线对应好通道;3、总线设置好地址位。设置效果如图3、图4所示:图3触发设置图4属性配置五、IIC解码分析结果开始采集并存储一段数据,从而进行解析。1、数据段区域,体现了具体数据解析的波形于结果;2、可以通过波形显示设置调节波形观察的方式;3、通过波形缩放能够观察不同时间产生的具体帧传播内容;4、时间表显示区域则会把整个数据段的内容逻辑解析并转化。测试效果如图5所示:图5解码分析六、IIC解码数据查找1、查找总线:IIC;2、开始时间:Ds、A、B;3、结束时间:Dp、A、B。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro。

序列的每个步骤被称为一个序列步骤。每个序列步骤由两部分组成:条件和操作。条件是指布尔逻辑表达式,例如“IfADDR=1000”或“IfthereisarisingedgeonSIG1”。操作是指符合条件时逻辑分析仪应当执行的内容。操作的示例包括触发逻辑分析仪、转至另一序列步骤以及启动定时器。这类似于编程中的If/Then语句。触发序列中的每个步骤都被指定一个数字。执行的个序列步骤总是序列步骤1,但由于“转到”操作,剩余的序列步骤可以以任意顺序执行。执行一个序列步骤且布尔逻辑表达式均为假时,逻辑分析仪将采集下一样本并再次执行同一序列步骤于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一个序列步骤中的布尔逻辑表达式,那么在执行下一序列步骤之前总是采集另一样本。换句话说,如果一个样本符合序列步骤1的条件,在执行序列步骤2前将采集另一样本。这意味着一个单独的样本不可能符合多个序列步骤的条中的条件二者之间采集了新的样本,因此逻辑分析仪不会在采集样本#1时触发。可将此触发序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。触发序列中的多序列步骤暗示了“后接”。逻辑分析仪触发后,将不会再次触发。换句话说。PCle Gen 3协议分析仪/训练器找欧奥!

RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。内存深度设置为总采集内存的1/2。所有盒对都可用于采集数据。如果选择整个内存,则要用于时间标签存储的默认Pod是左边的盒对,但未分配总线或信号的任何Pod都是可以使用的。跳变定时模式,时间标签存储需要1个Pod或1/2的采集内存:跳变时序采样模式也需要时间标签存储。当选择小采样周期时。必须将一个Pod对保留用于时间标签存储。在这种情况下,不能使用1/2(或更少)的模块采集内存来替代该Pod。对于其他采样周期,内存深度和通道数的权衡与状态采样模式下的相同。也就是说,要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。状态模式采样位置、眼定位和眼图扫描同步采样(状态模式)逻辑分析仪与触发时钟沿的触发相似,因为它们都需要输入逻辑信号才可以在时钟事件前。ONFI v4协议分析仪/训练器找欧奥!茂名RFFE分析仪找哪家

分析仪厂家哪家好?欧奥电子好!揭阳SDIO分析仪电话

建立时间)和时钟事件后(保持时间)的一段时间内保持稳定,以便正确解释逻辑电平。组合建立和保持时间被称为建立/保持窗口。被测设备(由于其本身的建立/保持要求)可指定数据在某段时间内在总线上有效。这被称为数据有效窗口。一般情况下。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。多总线上的数据有效窗口小于总线时间周期的一半。要精确采集总线上的数据,需符合以下条件:逻辑分析仪的建立/保持时间必须在数据有效窗口内。图12有效采集窗口由于与总线时钟有关的数据有效窗口的位置根据总线类型的不同而有所变化,因此逻辑分析仪的建立/保持窗口的位置在数据有效窗口中必须是可调整的(相对于采样时钟。揭阳SDIO分析仪电话

上一篇: 揭阳UFS分析仪品牌

下一篇: 揭阳协议分析仪费用